Inside The World Of Advanced Packaging

The CEO of NHanced Semiconductors discusses Moore’s Law, advanced packaging, chiplets and Foundry 2.0.

By Mark LaPedus

Bob Patti, president and chief executive of NHanced Semiconductors, sat down with Semiecosystem to discuss the future of Moore’s Law, advanced packaging, chiplets and Foundry 2.0. Patti also outlined the expansion plans at U.S.-based NHanced, a pure-play advanced packaging foundry. The company’s manufacturing capabilities include 3DICs, chiplets, interposers and other technologies.

Semiecosystem: Who is NHanced and what is the company’s charter?

Patti: NHanced is focused on being a one-stop shop for advanced packaging, emphasizing engineering agility. Unlike major foundries, which prioritize high-volume clients, we cater to lower-volume, high-complexity needs. For instance, our processes support wafer reconstruction, optical and RF interposers, MEMS work, and 3D designs.

Our hybrid bonding capabilities are especially notable. By 2026, we expect to surpass TSMC in hybrid bonding capacity—assuming they don’t significantly expand. Of course, companies like Samsung, Sony, and Tsinghua Unigroup are larger players in this space, but we’re carving out a niche with superior yields and vertically integrated processes.

Semiecosystem: For years, chip vendors developed a new device. Then, vendors would develop a more advanced version of the device by having it manufactured in a new process every two or so years. The goal is to develop a device with more advanced functions at each generation. Some call this chip scaling or Moore’s Law. We hear traditional chip scaling is supposedly slowing and becoming more difficult at each node. What’s happening with traditional chip scaling?

Patti: Chip scaling has given us incredible gains in performance and reduced costs by orders of magnitude for decades, but we are approaching the limits of physics. Performance is mostly limited by interconnect now. The cost benefit of Moore's Law has plateaued, if not stalled completely. The only way to reduce costs now is to reduce transistor count, and to reduce transistor count, you have to stop packing more and more functions onto a single chip.

The direction the industry is starting to go is to use chiplets to tailor functionality to meet specific customer needs. So for example, ‘customer A’ gets three processors, ‘customer B’ gets four, ‘customer C’ gets 10, and ‘customer D’ may only need one. This way, customers start doing their own customization to hit different price points, essentially creating a new Moore's Law based on delivering functionality instead of more transistors for the same dollars. By taking transistors out of designs, you have an agile ability to make modifications to target much smaller markets.

Semiecosystem: Years ago, IC packages were relatively simple units that basically encapsulated a chip. In recent times, IC packaging, particularly advanced packaging, has become more important. Why? And what role does packaging play now?

Patti: Advanced packaging is now the key to progress. The economics are now intellectual property driven and engineering driven, and it's changing the way the semiconductor industry works. Previously, semiconductor fabs with the cheapest money and lowest cost of capital were the winners. Now it’s shifting to engineering as the primary driver.

The major foundries are making difficult choices on the customer projects they take on. The opportunity cost is high if extensive engineering is required. As the industry moves to an engineering-heavy fab-light approach, the U.S. moves into a much better position, because cost of capital becomes a secondary consideration. With the engineering talent available, an agile foundry business can take on a thousand designs a year with low to medium volumes rather than a hundred designs at high volumes. Of course, the major foundries will still thrive, catering to that smaller set of customers that need high volumes, and they’ll also be manufacturing the chips and chiplets needed by the new agile foundries.

Advanced packaging technologies make it possible to achieve 2.5D interposer packages that are thinner than a Euro. Source: NHanced

Semiecosystem: You’ve talked about something called Foundry 2.0. What is that?

Patti: Foundry 2.0 isn’t just a new label; it’s a whole new way of thinking. Traditional foundries like TSMC and UMC are all about volume and scale—they’re built to manufacture large numbers of identical chips, based on high volumes and pushing the bleeding edge of transistor technology. That’s what I’m calling Foundry 1.0.

Foundry 2.0, on the other hand, focuses on customization—sourcing the best components from existing manufacturers and using advanced packaging and additive manufacturing to create highly specialized devices. It’s about flexibility and speed to market, which are crucial in today’s rapidly changing landscape.

Foundry 2.0 builds semiconductors that are based on advanced packaging and high-customization oriented manufacturing. It uses a new set of advanced packaging tools, including hybrid bonding, flip chip, interposers, 2.5D, and 3D true heterogeneous integration. Foundry 2.0 will also drive the incorporation of new materials, such as GaN, GaAs, indium phosphide, and—for photonics—lithium niobate and barium titanate oxide, or BTO.

Semiecosystem: Over the years, I assume you’ve been approached by many companies who want to develop a sophisticated and advanced 2.5D or 3D package. They may or may not have expertise here. What are some of the issues and considerations one must think about before developing these types of advanced packages?

Patti: Engineering is central to our approach. Traditional high-volume foundries face opportunity costs when taking on low-volume, engineering-intensive projects. That’s where we step in. We’re an engineering-first company supported by a foundry, not the other way around.

This allows us to handle a wide variety of designs—from boutique interposers to complex heterogeneous integration—while ensuring quick turnarounds. It’s about giving customers more for less, especially as they demand higher levels of customization.

Semiecosystem: In recent times, we’ve heard a lot about chiplets in the packaging world. Several companies have adopted the chiplets concept. Yet, it’s still not a mainstream technology. What are the challenges with the chiplets concept and what’s holding this back?

Patti: Chiplets are transforming the market. Moore’s Law is no longer the cost-reduction driver it once was. Instead, customization through chiplets—modular building blocks tailored to specific needs—is enabling more targeted designs.

For example, instead of packing every feature into a single chip, manufacturers can create single-feature chiplets optimized for different markets. This shift favors agile, engineering-driven businesses like ours. We excel in rapid customization, which allows customers to achieve cost reductions without compromising performance.

One of the roadblocks to adopting chiplets as a mainstream technology is the lack of agreed-upon standards. I like to say this: ‘The good thing about universal chiplet standards is that there are so many to choose from.’ When each manufacturer is using different protocols, it makes integration more difficult and expensive. At NHanced, we focus on creating solutions that streamline this integration, allowing different chiplets to work together more effectively. It’s about removing friction points and making the process more efficient for our customers.

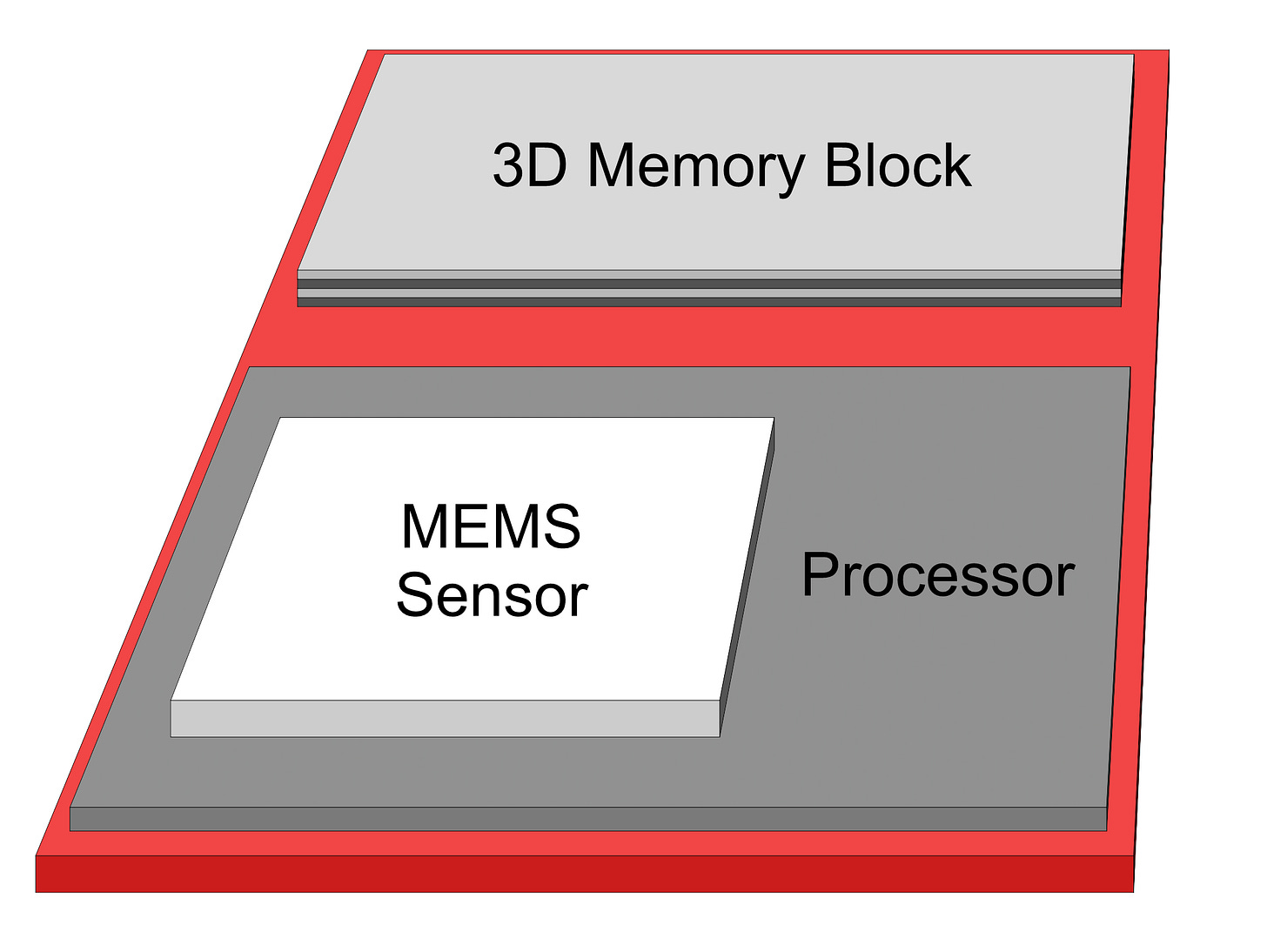

Chiplets allow the integration of various and different functional dies on a substrate or into a 3D chip structure. Source: NHanced

Semiecosystem: Besides advanced packaging, there is a lot of activity in the compound semiconductor market. What’s happening with packaging here?

Patti: Compound semiconductors are a driving factor for advanced packaging. Materials like GaN and SiC have more than an order of magnitude performance gains in specific functions when compared to silicon. The Achilles’ heel has always been how to tightly integrate these advanced materials with standard CMOS, which is required for the processing and control of the compound semi components. When compound semi devices are separately packaged with millimeters or centimeters of wire interconnection to the control and processing CMOS circuits, much of the potential gains are lost.

Advanced packaging directly addresses and eliminates the wiring issues. However, combining these exotic materials can be very challenging. First of all, the CTE mismatch must be dealt with. Many exotic materials contain gold interconnect, which is poisonous to CMOS. Exotic materials also tend to be more fragile and have other physical characteristics that present manufacturing challenges. Like most things that offer huge gains, there is real work required to realize them.

Semiecosystem: Let’s get back to NHanced. Can you briefly talk about your expansion plans?

Patti: We’re growing significantly. Our Indiana facility will soon house a new interposer fabrication line capable of 5,000 wafers per month, operational by early Q1 of 2025. This complements our existing line in North Carolina, which is ramping up to two and then three shifts. By 2026, we’ll add two more 5,000 wafer lines in North Carolina—one for 300mm and another for 200mm wafers. Altogether, we’re targeting 15,000 to 16,000 wafers per month by the end of 2026.

Additionally, our North Carolina facility is expanding into an adjacent 30,000-square-foot building in order to support our growing capabilities in TSV (through-silicon via), hybrid bonding, and low-volume development work.

Semiecosystem: There are a number of OSATs in the United States. But in general, a large percentage of the world’s packaging production capacity is located in Asia. But there are ongoing geopolitical tensions in Asia, causing many to realize that the United States needs more semiconductor and packaging production. The CHIPS Act is designed to bring more chip production to the U.S. Any thoughts about reshoring packaging and/or chip production in the U.S.?

Patti: I think the CHIPS Act was in many ways the right thing to do. We do have to onshore, or re-shore, some Foundry 1.0 fabs back to the U.S. We really had to make the CHIPS Act investment; if we didn't, the industry would leave to find a more hospitable business environment. There are government investment programs all around the world. Europe, China, Japan, Korea, and India are ramping up their own versions. In all, half a trillion dollars are available in incentives worldwide; our CHIPS Act funding, including the tax incentives, is only 20% of that total.

That being said, I do think that the U.S. CHIPS Act has been concentrated on winning the last war, not winning the next war. We need to invest in technologies and processes that aren’t being done in Asia that make economic sense, and that advance the state of the art for semiconductor manufacturing. Nobody wants to build a huge factory in the U.S. to do high-volume wire bonding or flip chip that is identical to what they already have overseas.

The growth opportunity for new investment is in advanced packaging, chiplets and heterogeneous integration—things that don’t already exist on a large scale, either here in the U.S. or around the world. That is the key to achieving the most bang for the buck.

So, where is the barrier to entry in this new semiconductor market space? If it’s the availability of engineering talent, then the U.S. is in a great position, because we have a wealth of engineers. When other companies build their workforce, they primarily focus on technicians. NHanced is unusual; our engineers outnumber the techs, rather than the other way around.

Ironically, NHanced didn’t initially qualify for CHIPS Act funding because we're already in the U.S., and not offshore, which is a different problem.

Semiecosystem: NHanced recently took delivery of a next-generation hybrid bonding system from Besi. What types of packages can one build using hybrid bonding? Is it a game changer?

Patti: For hybrid bonding, we have 300mm capability with high throughput, thanks to our new state-of-the-art Besi bonding system. It gives us 200 nanometer 3-sigma alignment to support high precision die-to-wafer bonding. This is a high-volume solution with high yield. We expect at least four nines yield. I predict we'll get better than five nines yield (99.999%) for hybrid bonding, positioning us as a leader in this area, especially for next-generation chip designs requiring robust performance and cost efficiency.

Semiecosystem: What about thermocompression bonding?

Patti: We do some thermocompression bonding. It’s halfway between conventional flip chip and hybrid bonding, but it's a relatively niche area. In the early 2000s before NHanced started, when I was at Tezzaron, we started with thermocompression bonding, but we moved to hybrid bonding because the yields and throughput were better. Hybrid bonding will eventually become the technology of choice, but there are some hoops to jump through to make it work. Thermocompression bonding will still have its uses down to a certain bump pitch or in certain applications.

Semiecosystem: NHanced is developing its own interposers. What is that all about? Is this for 2.5D applications?

Patti: Interposers are a critical focus for us. Today, most high-volume interposers come from UMC using 65nm processes, which work well for high-demand applications. However, our approach is different. We’ve developed proprietary interposer processes that enable eight to twelve wiring layers and thicker designs—200 to 300 microns—that handle better in low-volume production. We are also building optical interposers and RF interposers.

We foresee a shift from silicon to glass substrates in the next few years. Glass offers better performance and scalability for advanced designs. While glass panels may be the long-term goal, wafer-based glass interposers are more viable in the short term due to existing manufacturing capabilities. Our interposer line will be ready in early Q1 of next year, and we'll be able to run about 5,000 wafers a month.

Semiecosystem: NHanced offers something called Micro-Transfer Printing (MTP). What is that? Does that involve chiplets?

Patti: MTP is an extension to hybrid bonding, in my opinion. MTP uses elastomeric stamp transferring of ultra-tiny chiplets. These micro-chiplets could be as small as 5 x 5 microns. The stamp allows dozens or even hundreds of individual components to be gang transferred or printed at the same time. We see applications for integrating individual power transistors and creating displays. One promising usage is adding micro-chiplet buffers and drivers to glass panels for 2.5D integrations. This gives the performance of active interposers with the yields and costs of passive interposers.

(Send comments to: mdlapedus@gmail.com Semiecosystem reserves the right to post and edit comments.)