Issues and Challenges with IC Packaging

The CEO of Promex Industries and QP Technologies talks about traditional chip scaling, chiplets, mature package types and reshoring, as well as the issues in packaging for medical devices.

By Mark LaPedus

Dick Otte, chief executive of Promex Industries and QP Technologies, sat down with Semiecosystem to discuss traditional chip scaling, chiplets, mature package types, and reshoring, as well as the issues in packaging for medical devices and compound semiconductors.

Semiecosystem: Can you tell us about Promex Industries and the company’s charter? Also, please tell us about QP Technologies and how it fits in the company. What types of packages do you offer?

Otte: Both Promex, located in Santa Clara, Calif., and QP Technologies, located in Escondido, Calif., near San Diego, are contract manufacturers providing assembly services. Promex has no products of its own; everything we build is designed by our customers, often with guidance from us about manufacturing solutions. Our two factories have similar chip packaging capabilities but differ in package portfolios and the markets they serve. Every product we build incorporates bare semiconductor die. Most products are physically small, meaning you can hold dozens in one hand.

QP Technologies specializes in quick-turn chip packaging, often working with IC engineers developing new chips. QP Tech can put 25 die from a customer wafer in any standard chip package in five days. The division invoices around 400 customers in a calendar year, utilizing standard industry processes and packages.

Promex, however, develops custom assembly processes for products that contain at least one chip and usually other electronic and non-electronic components, such as optical components, chemistries, liquid channels, ultrasonic devices, and MEMS chips. Many products are for medical or biotech applications where process validation is required. Process customization is necessary because non-electronic parts will often not tolerate standard electronic assembly processes. Once a process is validated, Promex usually builds the product for years.

Semiecosystem: For years, semiconductor companies have followed the same basic formula. Companies develop a new chip. Then, at each new generation or process node, companies develop a more advanced version of the chip. The goal is to develop a chip with more functions and lower power at each node. Some call this chip scaling. Today, traditional chip scaling continues, but it is supposedly slowing and becoming more difficult at each node. Any thoughts here?

Otte: Continual scaling, or making on-chip features smaller, is now in the range of two nanometers (nm), which is approaching the size of individual silicon atoms (~0.3nm). Transistor functions are bulk phenomena and require a few atoms organized in a specific way. You cannot make a transistor with fewer than two atoms – probably more like six to 10 – so at the 2nm node, we are close to making the smallest transistor possible.

Once we reach that size, the way to increase the number of transistors per unit volume is to stack them. That is being done in semiconductor memory chips with over 128 layers now in production. Once that method is maximized, we will not be able to increase any further the number of functions per unit volume of die.

Semiecosystem: Many years ago, IC packaging was an afterthought in the semiconductor industry. The IC packages themselves were relatively simple units that encapsulated the chips. In recent times, IC packaging, particularly advanced packaging, has become an important part of the semiconductor industry. Why? And what role does packaging play now?

Otte: In the ’80s, chips were made utilizing the ~100nm or larger nodes. These transistors were relatively large and could inherently drive signals through a long interconnection to another chip. As lithography improved, transistors and other features got smaller, so the length of interconnect that the smallest possible transistor could drive declined.

Eventually, large transistors like those in the older nodes are needed to drive off-chip interconnects. Chiplets avoid the need for these large transistors by utilizing very short connections to other die. The short interconnects are in bridges and interposers for stacking of die.

Semiecosystem: In the packaging world, chiplets are grabbing the headlines today. What are chiplets and what are the benefits?

Otte: A chiplet is a semiconductor die that is designed to be interconnected with other die with very short interconnects. Traditional die are made with output drivers able to provide enough power to drive many centimeters of copper interconnect. This requires large transistors. Chiplets leave out these output drivers and assume the amount of power needed is much lower because the interconnect to other chips is only a few millimeters or less.

Semiecosystem: Is it safe to say that the chiplet concept isn’t really a mainstream technology today? What are the challenges with the chiplets approach?

Otte: Whether or not chiplets are a mainstream die configuration is a matter of opinion, influenced by chiplet enthusiasts. Chiplets today are largely going into products built by TSMC, GlobalFoundries, Intel and a few other large organizations that are vertically integrated, and thus able to design all of the parts that go into the end product incorporating chiplet die. They control the chiplet die, other die, the interposer or substrate, assembly and test of the product. Eventually, chiplet standards will emerge, and then a merchant market for chiplets and interposers is likely to follow.

Semiecosystem: Advanced packaging as well as chiplets tend to grab the headlines. But the bulk of today’s chips are still housed using legacy and more mature package types, right? I assume there is still demand for the more mature package types. Why?

Otte: Yes, 95%-plus of die shipped are in traditional packages: QFNs, ball grid arrays (BGAs), dual in-line packages (DIPs), small outline ICs (SOICs), and others. Relatively few die go into multi-die packages or into chiplet packaging. However, the value/price/cost of chips in emerging, custom and chiplet packages is often much higher than in the established packages. The demand for a specific package type declines slowly because there are always products designed years, or even decades, ago that are still in production.

Semiecosystem: Promex/QP offers several types of packages. Some of these offerings are more mature package types, such as QFN. QFN has been around for some time. Why do you offer QFN? What is QFN and what are the benefits? What are the main applications for QFN?

Otte: QFN stands for Quad Flat No-lead package. We provide QFNs because that is what customers ask for. The QFN is the most standard package for die today. If a suitable QFN package is available for a die or electronic part, that is usually what the manufacturer will choose. QFNs come in sizes from 2mm x 2mm with four leads, up to 12mm x 12mm with ~120 leads in standard formats. The standard thickness is 1mm. Most are built on a leadframe and wirebonded, but more complex packages are built on multilayer substrates.

They have a solid copper pad for the die that provides excellent thermal conductivity and dissipation. The leads are short, minimizing electrical parasitics. QFNs are the first choice for any die or electronic device because the equipment to build, test and assemble them is quite common, making that configuration the lowest cost.

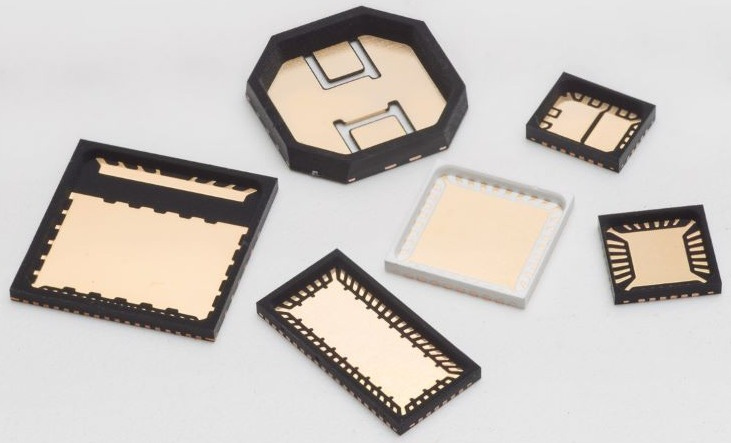

These custom QFN packages or Open-molded Plastic Packages (OmPP) come in a variety of sizes and are ideal for prototype, mid volume or production volume applications. Source: QP Technologies

Semiecosystem: For years, medical electronics has been an important field. What types of medical devices are involved here? What are some of the innovations in the arena?

Otte: The addition of electronics, especially chips, to gather data and process data from sensors, then communicate the result to the MD or patient is a major driver of devices we see. Today’s die can easily contain 100,000,000 transistors that have a lot of processing power and memory. Combining electronic components with devices that sense a condition in the body and devices that communicate results in heterogeneous integration – with all that implies about unique, custom processes – to accommodate these non-electronic parts. Additionally, devices are increasingly being designed to be smaller, both to minimize their impact when implanted in the body and to reduce the size of the instruments used in various medical and biotech applications.

Semiecosystem: What are some of the packaging issues and challenges in the medical device field?

Otte: The challenges are many, especially for devices that can cause harm or even death. Packaging issues include:

1. Building devices that are small to minimize the impact on the body. We see and build devices that are injected with a hypodermic needle.

2. Ensuring that the materials in implantables do not cause harm in the body by either: a) Excluding those materials; or b) Packaging them with fluid-tight containment.

3. Ensuring that the devices work.

The challenges include:

1. Finding a way to fund the multi-year development cycles required to get FDA approval.

2. Ensuring that the materials and processes used to build devices will be available for 10 to 20 years so that requalification is not required.

Semiecosystem: I believe you are doing work in the compound semiconductor field. What types of compound semis do you work with and what types of packages are involved here?

Otte: QP Tech does indeed see semiconductors other than silicon CMOS. Indium phosphide (InP) is often used for optical devices and is packaged with PIC, glass fibers, other optical components and chips. Gallium arsenide (GaAs) and gallium nitride (GaN) are used in large, heavy power devices that are designed to minimize electrical resistance and maximize heat transfer. Silicon carbide (SiC) is also used for power devices that sometime run at very high temperatures – such as 600 degrees C. These packages contain no organics, and all utilize brazing-like processes.

Semiecosystem: For years, the packaging market has been very competitive. A number of OSATs and foundry vendors compete in the market. Some companies are large, while others are small- to mid-sized vendors. I believe Promex/QP falls in the mid-sized category. Can you comment on the competition here? Is there room in the packaging market for mid-sized players?

Otte: Most things we package at QP Tech are there to save time versus ending the devices to Asia. The average job is priced around a few thousand dollars and is in and out in less than two weeks. At Promex, we work closely, often for 24 months, with design engineers to develop a very unique process for building what is often a complex or difficult-to-build device in volumes of hundreds to a million a year. Once developed, the customer stays with us onshore rather than undertake the added expense and time to develop the process again with an offshore, lower cost supplier. Work is done on a time-and-material charge basis or under a long-term contract with milestone payments.

Semiecosystem: The U.S. government is making a major effort to expand semiconductor and packaging production in the United States. The U.S. government is backing a major program called the CHIPS and Science Act. In recent times, the government has awarded several chip and packaging vendors with funding. Any thoughts on reshoring chip and/or packaging in the U.S. or the CHIPS Act?

Otte: The CHIPS Act resulted in a lot of discussion about joining together and working together among those in the industry. That alone has been a good thing and is helping the industry work together more. The government will be successful to some degree in reshoring wafer fabrication. The first question is, ‘What will be brought back: mainstream chips, low-cost chips, advanced technologies, only new semiconductors, etc.?’

There is also a need to package wafers and assembly die cut from them on substrates or interposers. Historically the industry sent wafers from the U.S. to Asia for packaging at low cost. Thus, the second question is, ‘Where will the new wafers fabricated in the U.S. be packaged? Can packaging and die assembly be brought back onshore?’ Time will tell as the new revitalized infrastructure continues to take shape.