U.S. CHIPS Program Launches Metrology Initiative

The goal is to address the challenges in metrology for advanced chips and packages. It has also funded next-gen metrology systems like CDSAXS and EUV scatterometry.

By Mark LaPedus

The CHIPS for America office has launched a new initiative to address the challenges in metrology, a critical chip manufacturing technology that generally flies under the radar.

The office has established a new community of practice, dubbed the CHIPS Metrology Community. The community will help address the growing challenges with metrology, which is the science of measurement. In the semiconductor world, metrology involves the measurement and characterization of tiny structures and materials in chips and packages using various equipment. Metrology, along with other technologies, helps determine the success or failure of a given chip line.

The CHIPS for America office is part of a major program that involves the CHIPS and Science Act. Spearheaded by the U.S. government, the CHIPS Act is designed to expand semiconductor production in the United States. The act also involves several R&D programs that are critical for U.S. competitiveness. CHIPS for America includes the CHIPS Program Office, responsible for manufacturing incentives, and the CHIPS Research and Development Office, responsible for R&D programs, that both sit within the National Institute of Standards and Technology (NIST) at the U.S. Department of Commerce.

The CHIPS Act involves $39 billion in grants for manufacturing and $11 billion in funding for R&D and workforce development. In recent times, the U.S. government has awarded select companies with grants and/or tax credits for use in building new fabs and/or expanding existing chip facilities in the U.S.

In 2022, the U.S. government established and funded the CHIPS Metrology Program under the CHIPS Act. This program recently launched a number of new and advanced R&D metrology projects (See below).

Metrology is a priority here and for good reason. Over time, semiconductors, or chips, have become more complex with smaller features. It’s become more difficult to measure and characterize the latest chips. So, chipmakers require new and more expensive metrology equipment types to address the challenges. This in turn drives up the cost of metrology in the semiconductor industry.

That’s why the CHIPS Act funded a metrology program. But metrology is a fragmented business with several disciplines. So, the industry needs to collaborate to one degree or another. That’s why the CHIPS for America office launched the CHIPS Metrology Community.

Participation in the CHIPS Metrology Community is open and available to members across the semiconductor industry, academia, consortia, and all stages of career levels, from engineers to executives.

Today’s chips are complex with smaller features. (Source: NIST)

Metrology challenges

The semiconductor industry is a vast and enormous business. In 2024, the semiconductor industry is expected to reach $611 billion in terms of sales, up 16% over 2023, according to the World Semiconductor Trade Statistics (WSTS) organization.

The semiconductor industry also consists of a plethora of companies competing in different markets. Some companies design and sell logic-based chips like AI devices, GPUs, FPGAs and processors. Other companies compete in the memory market, which includes 3D NAND flash memory chips, NOR flash chips and DRAM. The market also consists of other chip types, such as automotive devices, display ICs, power semiconductors, RF products and others.

Generally, to make a chip line of one kind or another, companies first design a chip product using specialized software tools. Then, a semiconductor company manufactures a given chip line in large facilities called fabs.

During the manufacturing process in a fab, a given chip line undergoes a number of process steps, which in turn creates a finished chip product. The most advanced chips may undergo 1,000 process steps or more in a fab.

Once the chips are manufactured in a fab, the devices are shipped to a different facility called a packaging house or an outsourced semiconductor assembly and test (OSAT) vendor. At these facilities, the chips are assembled into an IC package. An IC package is a product that encapsulated the chip. The chip-packaging process involves a number of steps.

During this entire manufacturing process in both the fab and packaging house, a chip line undergoes a number of inspection and metrology steps using different equipment. Inspection equipment looks for unwanted defects in chips. Metrology equipment measures the tiny structures and materials in chips, ensuring the devices meet a given specification. Both inspection and metrology equipment help ensure that a given chip line can be manufactured with good yields and few, if any, defects. If a given chip line is riddled with defects, it will likely fail or produce sub-standard results in a system.

Years ago, semiconductors were relatively simple devices. Thus, the inspection and metrology steps were rather straightforward in the fab and packaging house. In those days, semiconductor manufactures paid little attention to metrology.

That’s no longer the case. Over time, the chips have become more powerful and complex. In 1971, for example, Intel introduced its first processor--the 4004. The processor consisted of 2,300 tiny transistors. One of the key building blocks in a semiconductor device, a transistor amplifies or switches electrical signals within a chip.

In comparison, Nvidia this year introduced its new GPUs for high-end computing applications like AI. Manufactured using TSMC’s 4nm process, the GPU consists of a staggering 208 billion transistors on the same device.

Earlier this year, Cerebras Systems introduced its latest wafer-scale chip product, dubbed the Wafer Scale Engine 3. Built for training the industry’s largest AI models, the 5nm-based wafer-scale device incorporates 4 trillion transistors, delivering 125 petaflops of peak AI performance through 900,000 compute cores.

Cerebras’ product is a special case. Today’s semiconductors are typically smaller, chip-level products. In contrast, Cerebras’ device integrates the cores on a large square-like panel structure. The cores are linked together using an on-chip mesh-connected communications network. The panel itself consists of 46,225 square millimeters of silicon.

Nonetheless, as chip complexity increases, the ability to measure the tiny structures and materials in these devices has become more challenging. In many cases, the measurements are conducted at the angstrom level. An angstrom is 0.1nm. In packaging, the semiconductor industry typically doesn’t talk about angstroms. Packaging involves measurements at the micron-level, although that’s quickly moving to the nanometer realm.

Meanwhile, in the production flow, semiconductor manufacturers and packaging houses utilize a number of metrology equipment types to handle the latest chips and packages. Metrology tools utilize different techniques to measure and characterize chips. Some metrology tools are electron-based systems. Others use sophisticated optical techniques, while some are based on X-ray.

The current metrology equipment types are capable, but there are some gaps in the arena. For example, leading-edge chipmakers are migrating from today’s transistor types, known as finFETS, to a next-generation transistor type called gate-all-around (GAA). GAA is a complex 3D-like transistor structure with tiny features and materials. In GAA, some of the measurements required are extremely difficult, if not close to impossible, with today’s metrology tools. In the metrology world, there are also a growing number of challenges with the next wave of 3D NAND devices, DRAMs and other chips.

In fact, the CHIPS for America office has identified seven grand challenges that must be addressed in the metrology field. They are:

*Metrology for Materials Purity, Properties, and Provenance. Meet increasingly stringent requirements for semiconductor materials purity, physical properties, and provenance across a diverse supply chain through development of new measurements and standards.

*Advanced Metrology for Future Microelectronics Manufacturing. Ensure critical metrology advances keep pace with cutting-edge and future microelectronics and semiconductor manufacturing.

*Enabling Metrology for Integrating Components in Advanced Packaging. Provide enabling metrology spanning multiple length scales and physical properties for acceleration of advanced packaging for future-generation microelectronics.

*Modeling and Simulating Semiconductor Materials, Designs, and Components. Improve tools needed to effectively model and simulate future semiconductor materials, processes, devices, circuits, and microelectronic system designs.

*Modeling and Simulating Semiconductor Manufacturing Processes. Seamlessly model and simulate the entire semiconductor manufacturing process, from materials inputs to chip fabrication, system assembly, and end products.

*Standardizing New Materials, Processes, and Equipment for Microelectronics. Standardize the methods that will support and accelerate the development and manufacturing of microelectronics and advanced information and communications.

*Metrology to Enhance Security and Provenance of Microelectronic based Components and Products. Create the metrology advances needed to enhance the security and provenance of microelectronic components and products across supply chains and increase trust and assurance.

New metrology tools in R&D

As stated, today’s metrology tools are capable. But to address these grand challenges, the industry needs new breakthroughs. In response, the CHIPS Metrology Office is researching and developing several advanced metrology tool types. Here are just some of the R&D metrology tool projects here:

Critical Dimension Small Angle X-ray Scattering (CDSAXS)

In the fab, it’s important to measure the critical dimensions (CDs) of a given chip line. You need to measure the height, length and width of a structure. Generally, the industry uses various tools to measure the CDs of a chip structure. For complex devices, one metrology tool type, called optical CD (OCD), is the primary system used to measure the CDs in chips. Other metrology tools are used, as well.

OCD uses a technique called scatterometry to measure the feature sizes and shape structures in chips. But optical scatterometry is reaching its fundamental limits, according to NIST, an agency of the U.S. Department of Commerce.

In response, NIST and others are developing a technology called CDSAXS for next-generation dimensional metrology. CDSAXS, an X-ray technique, is used for 3D NAND applications today. But the technology is limited and too slow for logic devices. Under the CHIPS Metrology Program, researchers will expand the development effort at NIST for CDSAXS to address critical industry needs for in-line dimensional metrology.

NIST has developed a method called Critical Dimension Small Angle X-ray Scattering (CDSAXS) for next-generation dimensional metrology. Source: NIST

Advanced analytical electron tomography

Other CD metrology tools are also used in fabs. For example, the semiconductor industry uses transmission electron microscopy (TEM) and scanning transmission electron microscopy (STEM). Both are used for identifying structural and morphological characteristics of a device.

However, TEM and STEM imaging methods struggle with complex semiconductor device architectures, according to NIST. Under the CHIPS Metrology Program, researchers will develop atomic-resolution methods for complex semiconductor devices via electron tomography.

EUV scatterometry

Today, chipmakers use a combination of electron scanning modalities, OCD and other techniques to measure structures. TEMs are also used. CDSAXS is used in some cases.

But the industry needs a new system, which can measure beyond visible and ultraviolet wavelengths. This involves the spectral region from 10nm to 150nm. With funding from the CHIPS Act, researchers hope to develop novel extreme ultraviolet (EUV) optics, tabletop sources, and methodologies for inspection and process control. Today, though, no such tool exists.

EUV scatterometry. Source: NIST

Atom probe tomography (APT)

Other metrology tools are used for more specific applications in the semiconductor industry today. One tool type, APT, is an analytical system capable of providing 3D atomic maps of any element in the periodic table with sub-nm spatial resolution.

APT is becoming an important tool in fabs. However, today’s APT systems are sometimes inadequate, according to NIST. Under the CHIPS Metrology Program, researchers will make advancements for APT tools.

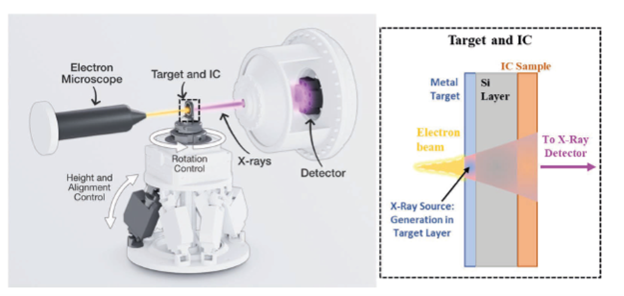

Element-Specific X-ray Imaging

Today, X-ray computed tomography (CT) is used for 3D characterization of subsurface feature sizes and shapes in chips. The most advanced spatial resolution is achieved using X-ray synchrotron beamlines, which is expensive.

Under the CHIPS Metrology Program, researchers hope to develop an advanced X-ray CT instrument for 3D, element-sensitive imaging at the micrometer to nanometer ranges.

The proposed instrument (left) utilizes a focused electron beam incident on a metal target and integrated circuit (IC) or semiconductor sample. Generated x-rays are attenuated by the sample before being detected and used to generate a 3D image. Inset (right) shows a schematic of the metal target and sample. Credit: Sean Kelley/NIST

Nanocalorimetry

Nanocalorimetry measures the thermal properties of small samples at fast rates. MEMS-based differential scanning calorimeters (DSC) and scanning probe calorimeters are used for this work.

Under the CHIPS Metrology Program, researchers would like to build upon today’s nanocalorimeters. The goal is to develop systems that directly measure transition temperatures, reaction temperatures and specific heat capacity of nanoscale materials.

Hybrid advanced packaging metrology

Advanced bonding tools enable 2.5D/3D packages. They are used to bond together different devices in chip-to-chip and chip-to-wafer applications. In the CHIPS Metrology Program, researchers hope to develop a scientific understanding of the bonding processes. This may provide a predictive framework, which impacts chiplet manufacturing.

Scanning probe-based metrology

Advanced packages, such as system-in-package (SiP) and others, are prone to thermal challenges and mechanical incompatibilities among the various interfaces and building blocks of the package. Currently, there are no established methods to perform microscale thermomechanical measurements here. In R&D, researchers are working on indentation and scanning probe-based measurement techniques for the thermo-mechanical properties of materials and structures used in advanced packages.

To be sure, the industry needs new breakthroughs in metrology. But it’s very expensive to develop next-generation tools. And it’s unclear if all of the R&D projects will result in real products.

It's a risk worth taking, though. The industry needs new metrology techniques, if it really wants the next wave of chips and packages.