U.S. CHIPS Program Launches Metrology Data Exchange; Funds Small Businesses

The CHIPS program has launched a new metrology data exchange, and announced funding awards for small businesses in the metrology and other fields.

By Mark LaPedus

The CHIPS for America program and other U.S. government agencies are doubling down on its efforts to develop new breakthroughs in metrology, a key technology used in the production of semiconductors.

In the latest efforts, the CHIPS for America program and others have launched a new metrology data exchange program, and announced funding awards for U.S.-based small businesses, many of which are developing a new class of metrology systems and other products. Both programs are designed to bolster the U.S. semiconductor ecosystem with some national security implications.

Metrology, which is the science of measurement, is an important part of the semiconductor industry. Basically, in a production facility, semiconductor manufacturers install various types of metrology equipment, which are used to measure the tiny structures in chips. Metrology equipment, along with other systems, helps ensure that a chip line meets a given specification and can be produced with good yields.

Nonetheless, in a recent announcement, the CHIPS for America program has released a beta version of a new data exchange initiative called the Metrology Exchange to Innovate in Semiconductors (METIS). The exchange will make research available to various entities, a move that could help accelerate new innovations in metrology. METIS will be available in a format that guards intellectual property and protects U.S. security.

Then, in another announcement, the U.S. Department of Commerce has awarded nearly $5 million to 17 small U.S.-based businesses. Each business will use the funding to explore the technical merits or feasibility of developing new products or services in the semiconductor field, including metrology equipment, simulation software and supply-chain tools. (See below for a description of some of the award-winning projects.)

The data exchange program and the small business awards are designed to support the CHIPS for America program and its ongoing efforts to expand chip manufacturing in the U.S. For years, the U.S.’s share of worldwide semiconductor manufacturing capacity has declined at an alarming rate. Today, the U.S. is dependent on Asia for the production of a large percentage of its chips, which is problematic for U.S. national security and the nation’s competitiveness.

In response, the U.S. government in 2022 launched a new program called the CHIPS and Science Act, which is designed to expand the production of chips and bolster the semiconductor ecosystem in the U.S. The CHIPS Act involves $39 billion in grants for manufacturing and $11 billion in funding for R&D and workforce development. Recently, the U.S. government has awarded select companies with grants and/or tax credits for use in building new fabs or expanding existing chip facilities in the U.S.

The CHIPS for America program, which is responsible for implementing the CHIPS Act, consists of two offices. The CHIPS Research and Development Office is responsible for R&D programs, while the CHIPS Program Office is in charge of manufacturing incentives. Both offices reside within the National Institute of Standards and Technology (NIST) at the U.S. Department of Commerce.

Besides chip manufacturing, the CHIPS for America program is also interested in funding various R&D programs, including metrology. In fact, the program has funded over $190 million across over 40 projects, helping to develop new measurement instruments—and for good reason.

Over time, semiconductors, or chips, have become more advanced and faster with more functions. The chips have also become more complex with smaller features. As a result, it’s becoming more difficult to measure and find the defects in the latest chips. So, semiconductor manufactures require new and more expensive metrology equipment types to address these challenges, but there are still some major gaps.

Metrology challenges

The semiconductor industry is a complex business with several facets. Semiconductors are tiny devices that incorporate complex electronic circuitry, which enables the part to perform different functions in a system.

The semiconductor industry produces a plethora of different chip types. Each chip has a different specification and application. Chips are used in a multitude of systems, such as appliances, cars, computers, medical equipment, smartphones and others. A car, for example, may incorporate from 1,000 to 3,000 chips, according to Polar Semiconductor.

Each chip incorporates a multitude of different and tiny building blocks. Transistors, one of the key building blocks in chips, are tiny structures that act like electronic switches in devices. Today’s advanced chips have billions of tiny transistors in a single device.

Generally, to make a chip line, a company first designs a specific chip product using specialized software tools. Then, in a fab, a semiconductor company manufactures that chip line based on the specifications of the design.

This isn’t a simple process. In the chip-manufacturing process, a chipmaker first obtains a round silicon-based wafer from a silicon wafer supplier. The most common wafer sizes are 200mm or 300mm in diameter. Then, the chipmaker takes the wafer and subjects it to a multitude of process steps using various equipment in the fab. A complex chip might undergo a 1,000 or more process steps in a fab.

These process steps create a multitude of finished chips, or dies, on each wafer. A wafer may consist of 300 to 400 separate dies, but this largely depends on the size of the chip. Once the chips are manufactured in a fab, the devices are shipped to a different facility. Here, the dies on the wafer are diced, and then assembled into an IC package. An IC package is a product that encapsulates the chip.

During this entire manufacturing process, a chip line undergoes a number of rigorous inspection and metrology steps using different equipment. Inspection equipment looks for unwanted defects in chips. Metrology equipment measures and characterizes the tiny structures and materials inside a chip, ensuring the devices meet a given specification.

For years, the inspection and metrology steps were relatively simple processes for chipmakers. That changed almost overnight.

In the 2010s, the semiconductor industry witnessed some major breakthroughs in both logic and memory devices. For example, suppliers of NAND flash memory moved from a planar to a 3D structure, enabling more storage density in a single device.

There were also several breakthroughs in the logic chip arena. Up until the 2010s, Intel, Samsung, TSMC and many others manufactured various types of chips, which incorporated tiny planar transistor structures. The chips themselves were somewhat complex parts that could perform amazing tasks at high speeds.

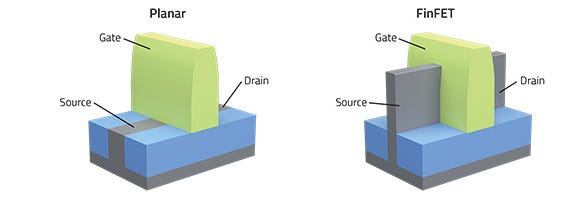

A planar transistor consists of a source and a drain structure on each end of a substrate. A gate structure resides in the middle. In operation, a gate voltage establishes a field. This in turn allows or blocks a current to flow between the source and drain. (Source of the image: Lam Research)

Generally, though, planar transistors inside these chips were relatively simple, 2D-like structures with large feature sizes. Thus, it was (and still is) relatively straightforward to measure and characterize planar transistors and other structures inside a chip.

Generally, in a fab, chipmakers only used a few metrology equipment types to measure and characterize planar transistors and other structures inside of the chip. For this, chipmakers mainly use a critical-dimension scanning electron microscope (CD-SEM) and an ellipsometer. A CD-SEM is a system that takes top-down images of a sample. An ellipsometer is an optical-based system, which measures a change in polarization as light reflects or transmits from a material structure, according to J.A. Woollam, a supplier of spectroscopic ellipsometry tools.

That all changed in 2010s. At the time, the planar transistor reached its physical limit at the so-called 20nm process node. Planar transistors are still used for chips at the 20nm node and above. A process involves a series of specific steps and guidelines to manufacture a given chip line in a fab. The node number (i.e. 20nm) refers “to a specific generation of chips made in a particular technology,” said David Schor of WikiChip, a technology site.

Nonetheless, the industry required a new transistor type for high-performance chips. In 2011, Intel migrated to a new and faster transistor type called the finFET at the 22nm node. Later, GlobalFoundries, Intel, Samsung, TSMC and others migrated to finFETs.

“As compared to prior planar transistors, the fin, contacted on three sides by the gate, provides much better control of the channel formed within the fin,” explained Nerissa Draeger, director of Open Innovation at Lam Research, in a blog.

Planar transistor vs finFET (Source: Lam Research)

Thanks to the finFET, the semiconductor industry overcame a major roadblock, enabling vendors to developed new and more advanced chips for several generations. Today’s AI chips and processors are faster with more functions. Today’s most advanced chips are manufactured using the so-called 3nm process node.

These chips are also more complex. To enable faster, low-power chips at each new generation, semiconductor manufacturers face a daunting challenge—they need to cram more transistors and other functions all in the same device.

For example, in 2020, Nvidia introduced the A100 GPU. Fabricated on TSMC’s 7nm manufacturing process, the GPU incorporates 54.2 billion transistors on the same device. This year, Nvidia introduced its new GPUs for high-end computing applications like AI. Manufactured using TSMC’s 4nm process, the GPU consists of a staggering 208 billion tiny transistors on the same device.

So at each turn, semiconductor manufacturers need to shrink the size of the finFET transistor and other functions. Thus, at each new generation, chips that incorporate finFETs have become more difficult and expensive to manufacture.

It's also harder to measure and characterize the finFETs at any generation. Unlike planar transistors, which are simple 2D structures, finFETs are tiny 3D-like structures with complex material sets. For example, TSMC’s latest 3nm finFET process, called N3E, consists of a 48nm poly pitch, a 26nm fin pitch, along with a minimum metal pitch of 23nm, according to WikiChip. In comparison, based on planar transistors, TSMC’s 28nm process node consists of a 117nm contacted gate pitch, along with a minimum metal pitch of 90nm, according to WikiChip.

Amid the advent of finFETs, the metrology requirements and challenges escalated. And so did the costs. For finFETs, chipmakers require more than just a few metrology tools. Generally, they require more than a dozen of different metrology tool types in both the fab and the laboratory.

In response, equipment makers stepped up to the challenge and developed a number of new metrology tools. According to GlobalFoundries, chipmakers require several different metrology tool types in five separate categories to measure and characterize finFETs, including:

*Critical-dimension measurements (atomic force microscopy, CD-SEMs, optical CD, transmission electron microscopy; scanning probe microscopy; various X-ray systems)

*Material composition measurements (atomic probe tomography, optical CD, secondary-ion mass spectrometry; various X-ray systems)

*Dopant composition measurements (atomic probe tomography, capacitance-voltage testing; secondary-ion mass spectrometry; various X-ray systems)

*Strain composition measurements (transmission electron microscopy, various X-ray systems)

*Electrical measurements (capacitance-voltage testing)

Each one of these metrology techniques are complex and could take tomes to explain. On its website, EAG Laboratories has chart and glossary that helps explains these analytical techniques. Click here for the site.

Going forward, the chips are expected to become more complex. For example, at the 3nm and/or 2nm nodes, leading-edge chipmakers are migrating from today’s finFETs to a next-generation transistor type called gate-all-around (GAA).

“Gate-all-around, or GAA transistors, are a modified transistor structure where the gate contacts the channel from all sides and enables continued scaling,” Lam’s Draeger said in a blog. “Early GAA devices will use vertically-stacked nanosheets. They are constructed of separate horizontal sheets, surrounded by gate materials on all sides. This provides improved channel control relative to finFETs.”

Planar transistor vs finFET vs GAA (Source: Lam Research)

GAA is a complex 3D-like transistor structure with tiny features and materials. In GAA, some of the measurements required are extremely difficult, if not close to impossible, with today’s metrology tools.

As before, metrology tool makers are expected to step up and meet the challenges with GAA. Leading-edge chipmakers will likely use the same metrology techniques as they did with finFETs. They also may need new metrology tools for GAA. Even then, there are expected to be some gaps.

CHIPS’ metrology efforts

That’s where the CHIPS Act fits in—the program will help fill in the gaps with new development programs and funding in the metrology arena. In 2022, for example, the CHIPS Metrology Program was established. This program is developing a number of new and advanced metrology systems.

NIST has developed a method called Critical Dimension Small Angle X-ray Scattering (CDSAXS) for next-generation dimensional metrology. (Source: NIST)

Meanwhile, in August of 2024, the CHIPS for America program established the CHIPS Metrology Community, which will facilitate data and knowledge sharing among various parties. Participation in the community is open and available to members across the semiconductor industry, academia and consortia.

In September 2024, the program released a beta version of METIS, a data exchange ecosystem developed by NIST that will give stakeholders access to CHIPS metrology research results and serve to catalyze breakthroughs in the arena.

In addition, the U.S. Department of Commerce awarded nearly $5 million to 17 small businesses under the Small Business Innovation Research (SBIR) Program. This is the first award for the CHIPS Research and Development Office. These Phase I SBIR awards are meant to establish the merit, feasibility and commercial potential for various R&D projects. Here’s just some of the award winners:

Octave Photonics

Octave Photonics, based in Louisville, Colo., specializes in the design, simulation, fabrication and packaging of nonlinear nanophotonic devices. It also develops nonlinear nanophotonics for use in metrology and spectroscopy applications.

“Our company is developing a new product based on a photonic integrated circuit that will enable high-speed detection of trace gases inside and outside of semiconductor fabrication facilities, including process contaminants and safety hazards,” said David Carlson, co-founder of Octave Photonics, in an e-mail exchange. “The SBIR program focuses on research and development of new technologies, so no product is shipping yet. However, our goal is to provide more versatile sensor infrastructure for both exquisite process control and environmental monitoring, enabling fabs to improve wafer yields, improve chip performance, and prevent costly downtime.”

Photothermal Spectroscopy

Photothermal Spectroscopy Corp. (PSC), based in Santa Barbara, Calif., has developed a technique called optical Photothermal Infrared (O-PTIR) technology. More recently, PSC has developed a simultaneous Infrared and Raman microscope and imaging system.

Under the CHIPS’ SBIR Phase I awards, PSC plans to extend the capabilities of its current systems. “Our breakthrough Optical Photothermal Infrared Spectroscopy technique (O-PTIR) solves a few fundamental problems with conventional FTIR and Raman technology. O-PTIR has sub-micron resolution and is used for advanced failure analysis of contaminants. O-PTIR has been adopted in failure analysis (FA) as it overcomes the limitations of existing Raman and FTIR techniques that were limiting their application in FA, such as fluorescence and spatial resolution,” said Dean Dawson, vice president of marketing and business development for PSC, in an e-mail exchange.

“For the SBIR program, we are proposing to extend our O-PTIR technique for high-speed thermal properties analysis and simultaneous chemical characterization of materials with sub-micron spatial resolution,” Dawson said. “Our new system would provide high resolution, fast measurement of material thermal properties to help manufacturers improve their process development times.”

The Provenance Chain Network

Based in Portland, Ore., the Provenance Chain Network is a developer of supply-chain tools. “Our SaaS Commercial Trust Platform (CTP) is in existence today and serves both government and commercial customers. The platform serves different industries and use cases and has specific applications that lay on top of the platform. Our technology helps a supply chain manage evidence of claims to support a requirement,” said Amy McDougall, chief commercialization officer of the company.

Sigray

Sigray, based in Concord, Calif., develops laboratory X-ray instruments for use in studying microstructures, chemistries and compositions. These instruments are enabled by ultra-high brightness X-ray sources and optics.

Under the CHIPS’ SBIR Phase I awards, Sigray is developing a new X-ray metrology system. “It uses an existing product, but makes a new product from it. Essentially, we are taking developments to our X-ray source and combining multiple sources to create a higher brilliance X-ray source,” said Sylvia Lewis, president of Sigray, in an e-mail exchange.

“It would enable a technique called CD-SAXS (Critical Dimension Small Angle X-ray Scattering) to meet the needs of next-generation transistor nodes, including gate-all-around,” Lewis said. “Right now, critical dimensions are mostly measured using the visible light approach called optical critical dimension (OCD), but it has significant limitations due to the longer wavelengths of visible light compared to X-rays. Researchers have convincingly demonstrated the power and advantages of CD-SAXS using synchrotron-based X-ray sources, but translating the approach from the synchrotron to the laboratory has been bottlenecked by the lower brightness of laboratory-based X-ray sources. This SBIR proposal aims to build an ultra-high brightness laboratory X-ray source to resolve this challenge.”

Tiptek

Tiptek, based in West Chester, Penn., develops and sells a line of probes and needles, which are used for scanning probe microscopy and other applications.

Under the CHIPS’ SBIR Phase I awards, Tiptek is developing a new product. “The technology is new and will result in a new product for Tiptek. It is not related to scanning tunneling microscopy (STM). STM only functions on conductive surfaces and semiconductors are mixes of conductive and insulating areas,” said Scott Lockledge, chief executive of Tiptek, in an e-mail.

“From a metrology perspective, this new technology allows failure analysis engineers to locate ‘soft’ defects. These defects are those that are difficult to find and cannot be located by traditional nanoprobing techniques. They are also more common in advanced node chips due to increased complexity and in new semiconductor architectures. Finding these defects requires high speed, alternating current methods as opposed to direct current nanoprobing methods typically used today. This is the technology that Tiptek will develop,” Lockledge said.

“This product does not exist today. The purpose of SBIR programs, including the CHIPS SBIR program, is to provide funding for focused and targeted R&D, that will directly lead to new products for small companies. The first phase lasts six months and is used to develop prototypes. The second phase is up to an additional two years, which provides for product development and launch,” Lockledge said.

Tech-X

Based in Boulder, Colo., Tech-X is a simulation software provider. Under the CHIPS’ SBIR Phase I awards, Tech-X will expand its recently-announced product called XSim, a simulation tool that addresses the complexities of both electromagnetic (EM) and photonic designs.

“Similar to analog circuits, which use EM waves at communications frequencies, components in photonics integrated circuits (PICs), which use EM waves at optical frequencies, are sensitive to layout and manufacturing variations—arguably more so,” said Scott Kruger, chief executive at Tech-X, in an e-mail exchange.

“Similar to their semiconductor counterparts, which transmit information using electrons, PICs transmit information using photons, and they also have to resolve signal integrity and parasitic losses. Designers of PIC components, therefore, have had to pioneer new design workflows. Currently, component designers have limited awareness of physical effects since they are limited to simulating extruded (as-drawn) GDS geometries, which under-represent important details of the as-manufactured PIC. As a result, they learn of the impact of physical effects like backscattering and parasitic interaction with other components much later, after prototype fabrication and during testing. This results in excessive design-of-experiments iterations and long loops of prototyping shuttle runs with their foundry partner, resulting in unpredictable timelines to market and a lack of flexibility to react to evolving requirements,” Kruger said.

“The solution to the problem requires industry cooperation: fabs ideally should measure and quantify the issues affecting design, and include it in their PDKs in a manner that design tools can use. By prototyping such a workflow by having a partnership between a PIC component designer (Dream Photonics), NIST for metrology, and the design tool (XSim from Tech-X), our goal is to demonstrate the acceleration of PIC development by having such a workflow and have it adopted by the PIC community,” Kruger said.

Here are a few other of the SBIR award winners:

*Direct Electron is developing a high-speed electron backscattering camera.

*Photon Spot is working on a cryogenic system for imaging applications.

*Laser Thermal Analysis is developing a hybrid atomic force microscopy instrument.

*Steam Instruments is working on an ion microscopy technology.