5 Takeaways From TSMC’s Global Open Innovation Platform (OIP) Ecosystem Forum

AI, TSMC’s roadmaps and HBM were among the highlights from the event. What else is happening?

By Mark LaPedus

During this past week, TSMC held its annual Global Open Innovation Platform (OIP) Ecosystem Forum, a large event that brings together TSMC, EDA companies, IP houses, and a few chip-assembly and test vendors.

The one-day event features a keynote session and multi-track presentations on various technologies. As in previous events, the conference also includes a large pavilion, where customers can actively engage with TSMC, the world’s largest foundry vendor, and its partners. I attended TSMC’s event on Wednesday (Sept. 25) in Santa Clara, Calif. TSMC also holds the same forum in other regions.

The idea behind the event is to get an update on TSMC’s technology roadmaps. The other goal is to get an update on the design readiness for TSMC’s technologies. Design readiness involves the EDA software tools and IP (intellectual-property) technologies, which are used to design and verify chip designs. Cadence, Siemens, Synopsys and others develop these critical EDA software tools.

For TSMC, the goal is to establish a robust design ecosystem around a specific process. In other words, TSMC must have the right EDA tools and IP technologies ready on time for a given process.

That way, TSMC’s foundry customers, namely chip vendors and others, know where to go and which EDA tools to use to develop their chips for a given process. All of this takes an enormous amount of collaboration, cooperation and investments among several parties.

Setting up a design ecosystem isn’t new. For years, TSMC has established design ecosystems for its other processes. Other foundry vendors do basically the same thing to establish their respective design ecosystems.

Nonetheless, here’s my five takeaways from TSMC’s recent Global Open Innovation Platform (OIP) Ecosystem Forum:

AI growth, challenges

At TSMC’s event, Partha Ranganathan, vice president and engineering fellow at Google, gave a keynote on AI. During the keynote, Ranganathan described the growth and challenges for Generative AI (GenAI), an advanced AI technology capable of generating text, images, videos or other data using large language models.

Today, the large language models for GenAI are growing two to three times per month, and roughly 10x per year, according to Ranganathan.

This in turn requires new breakthroughs in chip technology. To keep up with the demands for AI, the industry needs faster chips at lower power.

In a new blog, TSMC talks about how the industry can address these and other challenges. The blog can be found here.

TSMC’s roadmap is on track

TSMC’s advanced technology roadmap remains on track with no changes. That might not sound like news. In many respects, it isn’t news.

But not all leading-edge foundry vendors can say the same thing. For example, Intel recently revised its chip-manufacturing roadmap. The company scrapped one process and decided to focus on another technology.

It’s important to keep tabs on the various roadmaps from different foundry vendors. This is especially true for foundry customers, and their customer’s customers. That way, the various parties can keep track when a given process will move into production. This also determines when a given chip line is manufactured and whether the product will be ready in a timely manner.

Nonetheless, here’s TSMC advanced technology roadmap:

Year--Process

2024—N3E, N5A

2025—N2, N3P/N3X

2026—A16, N2P/N2X, N3A

So what does this all mean? First, these designations are marketing terms that are specific to TSMC. Other foundry vendors use different designations. It’s confusing to say the least.

For TSMC’s roadmap, each letter/number combo represents a specific process technology. A process involves a series of specific steps and guidelines to manufacture a given chip line in a large manufacturing facility called a fab. TSMC and other foundries are starting to use the letter “A” in their process designations, which means angstrom.

It’s confusing. Here, I will try to explain TSMC’s current and future leading-edge processes. Each process consists of a number of building blocks, which are used to manufacture chips.

Today, TSMC offers a range of processes, ranging from more mature to advanced technologies. The company’s most advanced process is based on a “3nm” technology. TSMC’s 3nm process incorporates tiny transistor structures called finFETs. Transistors, one of the key building blocks in chips, are tiny structures that act like electronic switches in devices. Today’s advanced chips have billions of tiny transistors.

FinFETs aren’t new. Starting at the 22nm node in 2011, Intel migrated to finFETs, which are used to develop high-performance chips. In 2013 or so, GlobalFoundries, Samsung and TSMC also migrated to finFETs at the 16nm/14nm nodes.

Fast forward. At TSMC, the company refers to its 3nm processes as N3 and N3E, as outlined in the company’s roadmap above. N3E is a more advanced version of N3. N3 moved into production in 2023, while N3E is ramping up in 2024.

In 2024, TSMC also moved into production with N5A, which is a faster version of its older 5nm process.

With these and other processes, TSMC has manufactured millions of chips for other companies. But the workhorse finFET transistor has finally run out of steam and reached its physical limits.

So, starting at the 2nm node (N2) in 2025, TSMC will migrate to a new transistor type called the nanosheet FET. It’s also known as a gate-all-around (GAA) transistor. Nanosheet FETs provide better performance than finFETs, but they are harder and more expensive to make in the fab.

TSMC is not the first company to make nanosheet FETs. In 2022, Samsung was the first company to ship chips using nanosheet FETs. Samsung introduced the technology at the 3nm node.

By the way, TSMC is expected to announce new versions of its 3nm process (3NP/3NX) in 2025. Those technologies are based on finFETs. Then, in 2026, TSMC is expected to roll out new versions of both its 3nm and 2nm processes.

What is A16?

In the second half of 2026, TSMC is expected to release A16, a new and more advanced process. Compared with its 2nm process, A16 offers an 8%-10% speed improvement with a 15%-20% power reduction. A16 offers a 1.07-1.10x boost in chip density.

Like TSMC’s N2 process, A16 is based on GAA technology (nanosheet FETs). But unlike N2, TSMC’s A16 process will incorporate a technology called backside power delivery. TSMC refers to its backside power technology as Super Power Rail (SPR).

Intel and Samsung are also moving to backside power delivery technology, which provides several benefits for future chip designs.

“All silicon chips today have power delivered from the frontside of the chip. This requires power to be delivered through over 10 layers of wiring, down to the transistor. There are two major limitations of this approach: valuable real estate on the chip must be allocated for power lines, and power is lost as it traverses the multiple levels down to the transistor,” according to a blog from Applied Materials.

“Backside power delivery refers to the technique of routing power supply lines on the backside of a semiconductor chip or integrated circuit (IC) instead of the traditional frontside. This approach increases logic density and improves power and performance,” according to Applied.

With the help of GAA and backside power delivery, TSMC and other foundry vendors are determined to develop new and more advanced processes, enabling the next wave of chips. Contrary to popular belief, chip scaling is moving forward. But to be sure, chip scaling is becoming more difficult and expensive at each node.

SK Hynix’ HBM roadmap

At TSMC’s event, SK Hynix gave a presentation and outlined its roadmap for the hottest memory product in the market--high-bandwidth memory (HBM). Besides SK Hynix, Micron and Samsung also sell HBM. HBM is a hot technology that is sold out until 2026.

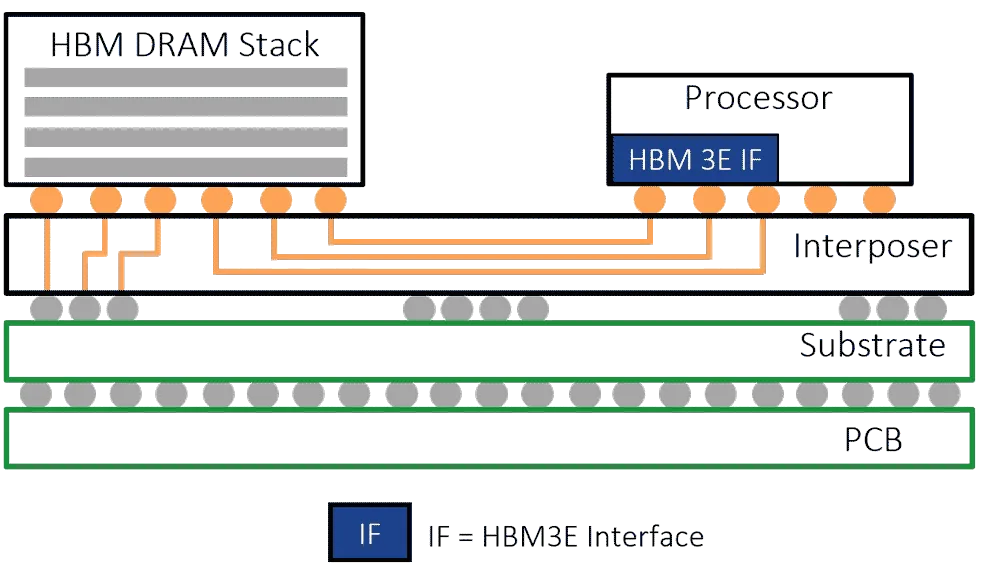

HBM is basically a stack of DRAM chips. To make an HBM product, a DRAM supplier first manufactures several DRAM devices. Then, those devices are vertically stacked on top of each other and connected. An HBM product might have 8 to 12 DRAM devices stacked on each other. The DRAM dies are then connected using tiny vertical wires called through-silicon vias (TSVs). The TSVs provide some of the electrical connections between each die.

HBM is an important part of today’s AI chip architectures. For example, Nvidia develops and sells GPUs, which are devices used to power the latest AI technologies. In Nvidia’s GPU architecture, the company combines a GPU, along with several HBM stacks, in the same package.

Nvidia’s GPU architectures are found in high-end computers called servers. These servers are processing today’s most advanced AI algorithms.

An HBM DRAM stack and a processor or GPU are situated on an interposer in the same package. HBM and the processor are electrically connected to each other. Source: Rambus

Meanwhile, at TSMC’s event, SK Hynix, the leader in HBM in terms of market share, outlined its roadmap in the arena. Today, SK Hynix and others are shipping HBM products based on the HBM3E standard.

Going forward, Micron, Samsung and SK Hynix are racing each other to develop HBM products based on the next-generation HBM4 standard. In R&D, SK Hynix is developing 12- and 16-die HBM4 products. The company also said that it will continue to use a proprietary manufacturing process called Mass Reflow-Molded Underfill (MR-MUF) for HBM4.

The company indicated that hybrid bonding is an option for HBM4, but it will continue to use MR-MUF here. In hybrid bonding, dies are stacked and connected using a copper-to-copper bonding process.

MR-MUF is a different way to connect the dies. SK Hynix is using this process for its current HBM products. In SK Hynix’ HBM process, the first step is to manufacture several DRAM dies. The dies must be electrically connected to each other in the stack.

To accomplish this task, tiny microbumps are formed on top of each DRAM die. Then, the bumps on one die are aligned to the bumps on another die. The same is true for the other dies.

At that point, SK Hynix implements its MR-MUF process. “Mass reflow is a technology that connects chips together by melting the bumps between stacked chips,” according to SK Hynix. “Molded underfill fills the gaps between stacked chips with protective material to increase durability and heat dissipation. Combining the reflow and molding process, MR-MUF attaches semiconductor chips to circuits and fills the space between chips and the bump gap with a material called liquid epoxy molding compound (EMC).”

Cloudy business conditions

There is a tremendous amount of innovation and design activity taking place in the semiconductor market today. At TSMC’s event, for example, several EDA companies announced new partnerships with TSMC, including:

*Ansys and TSMC have expanded their collaboration to leverage AI for advancing 3D-IC design.

*Cadence is collaborating with TSMC for advanced-node designs and 3D-ICs.

*Siemens has extended its collaboration with TSMC through multiple new development projects, product certifications and technology enablement for the foundry’s newest process technologies.

*Synopsys is collaborating with TSMC to deliver advanced EDA and IP solutions on TSMC's advanced processes and 3D-IC technologies.

Amid a wave of design activity, the overall semiconductor business is a mixed picture. In 2024, the semiconductor industry is expected to reach $611 billion in terms of sales, up 16% over 2023, according to the World Semiconductor Trade Statistics (WSTS) organization. Looking ahead to 2025, WSTS forecasts a 12.5% growth in the global semiconductor market, reaching an estimated valuation of $687 billion.

Overall, the high-performance computing (HPC) chip market has been a bright spot in 2024. HPC involves AI chips, processors and other products used in high-end computers like servers. One company, Nvidia, continues to see enormous demand for its GPUs with no signs of letting up.

Demand for chips in PCs and smartphones remain steady in some areas and sluggish in others in 2024. But chip demand for automotive and industrial applications has been lackluster at best this year.

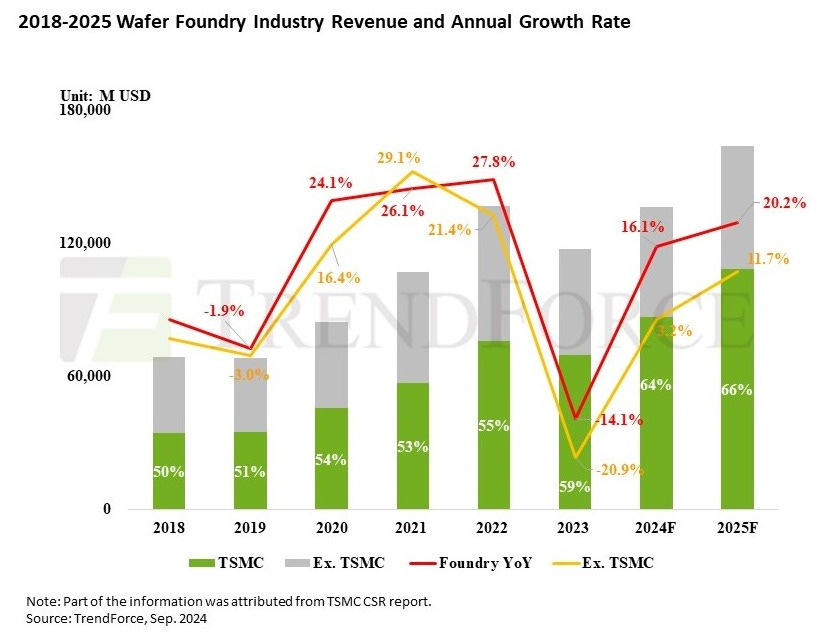

Meanwhile, in another forecast, the wafer foundry market is expected to grow by 20% in 2025, according to TrendForce. That compares to projected growth of 16% for 2024, according to TrendForce.

“This positive outlook comes despite the weak end-market demand for consumer products, which has led component manufacturers to adopt a conservative stocking strategy and made the average capacity utilization rate of wafer foundries fall below 80% in 2024,” according to the research firm. “Only advanced processes, such as 5/4/3nm nodes used for HPC products and flagship smartphones, have managed to maintain full capacity, and this situation is expected to persist into 2025. However, the visibility in the consumer end market remains low for 2025.”

As before, TSMC is dominating the foundry market in terms of share, according to the firm.