U.S. Launches Advanced Packaging R&D Projects

Updated: The U.S. government plans to invest up to $300 million for a trio of advanced packaging R&D projects in Georgia, California and Arizona.

By Mark LaPedus

The U.S. Department of Commerce is entering negotiations to invest up to $300 million for a trio of advanced packaging research projects in Georgia, California and Arizona.

The expected recipients for these projects are Absolics, Applied Materials and Arizona State University (ASU). Each entity will lead a project, which will propel the development of next-generation packaging technologies.

Each group is expected to obtain as much as $100 million. Up to $300 million in federal funding will be paired with additional investments from the private sector, bringing the expected total investment across all three projects to over $470 million.

Part of the funding is coming from the CHIPS and Science Act. For years, the United States’ share of chip-manufacturing capacity has dwindled. In response, the U.S. government in 2022 launched a new program called the CHIPS and Science Act, which is designed to expand the production of chips in the United States. The other goal is to provide funding for various chip-manufacturing technologies, such as lithography, metrology and now packaging.

There is some uncertainly with the CHIPS program, however. President-elect Donald Trump has been critical of the CHIPS Act, leaving many to wonder about the future of the program. For now, though, the CHIPS Act will remain in place. In a blog post, Counterpoint Research has provided an analysis of what the U.S. elections mean for the semiconductor industry and other sectors. Click here for the analysis.

The challenges

Nonetheless, packaging is an important part of the semiconductor industry. In the semiconductor process flow, a company designs a chip line using specialized software. Then, a chipmaker manufactures the chip line based on that design. Finally, the chip is assembled in a package.

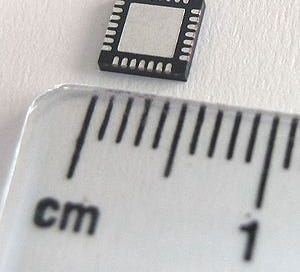

A package is a product that houses a chip and protects it from harsh operating conditions. There are different types of packages in the market. One segment, advanced packaging, is especially important. Advanced forms of packaging are used to boost the performance of a device.

For years, a multitude of companies have been developing and selling advanced packages. AMD, Apple, Intel, Nvidia and others develop chips, which are housed in advanced packages.

But there is more work that needs to be done in the advanced packaging arena. For one thing, the industry needs new breakthroughs to enable 3D packages. Basically, a 3D package stacks dies on top of each other.

For years, several companies have been developing and selling 3D-like packages. Now, the industry is working on the next wave of these products, but there are some issues. Manufacturing challenges, thermal issues and cost are just some of the challenges here.

At the same time, several entities are working on another form of advanced packaging called chiplets. In chiplets, the idea is to break up a large device into smaller dies. Then, the dies are assembled in an advanced package.

But there are several challenges to implement a chiplet-based design. In some respects, advanced packaging, including chiplets, are still too expensive.

New R&D projects

In any case, the industry continues to work on new breakthroughs in the arena. In the latest effort, Absolics, Applied Materials and ASU will lead the new packaging R&D projects in the U.S.

Absolics, based in Covington, Ga., is an affiliate of South Korea’s SKC. The company is developing glass core substrates for packaging in partnership with over 30 entities. Through its Substrate and Materials Advanced Research and Technology (SMART) Packaging Program, Absolics aims to build a glass-core packaging ecosystem. That project is located in Georgia.

Applied Materials, based in Santa Clara, Calif., along with a team of 10 collaborators, is working on developing a disruptive silicon-core substrate technology for next-generation advanced packaging and 3D heterogeneous integration. That project is located in Santa Clara.

ASU is leading the charge in developing the next generation of packaging through fan-out wafer-level-packaging (FOWLP). ASU’s team of over 10 partners is led by Deca Technologies. In addition to Deca, the team includes participation from several major semiconductor companies, including AMD, IBM, NXP, Synopsys, Saras Micro Devices and Analog Devices. These companies will provide crucial test chips and support for the technology's design, simulation and testing.

At the heart of this initiative is the ASU Advanced Electronics and Photonics Core Facility, where researchers are exploring the commercial viability of 300mm wafer-level and 600mm panel-level manufacturing. Click here for more about this project.