Intel, TSMC To Describe Next-Gen Transistors at IEDM

Imec, Kioxia, Samsung, SK Hynix, Sony and others will also present papers at the annual event.

By Mark LaPedus

Intel, TSMC and many others are expected to present papers on the latest breakthroughs in semiconductor technology at the upcoming 2024 IEEE International Electron Devices Meeting (IEDM) in San Francisco.

TSMC is expected to present a paper on its upcoming 2nm logic process, based on a new gate-all-around (GAA) transistor technology. Intel is also presenting a paper on its own GAA technology. In addition, Imec, Kioxia, Samsung, SK Hynix, Sony and many others will also present papers at IEDM, which takes place from Dec. 7-11.

IEDM is considered the largest forum where scientists and engineers come together to disclose their recent R&D work on various technologies. The 2024 IEDM technical program, supporting the theme “Shaping Tomorrow’s Semiconductor Technology,” will consist of more than 270 presentations plus a full slate of events, including an evening panel, focus sessions, tutorials, short courses and a supplier exhibit.

IEDM will also feature keynote presentations from the following luminaries: Y-J. Mii, executive vice president and co-chief operating officer at TSMC; Mark Fuselier, senior vice president of technology and product engineering at AMD; and Elif Balkas, chief technology officer at Wolfspeed.

Advanced logic

A multitude of companies will also present papers at IEDM. In many respects, IEDM provides a sneak peak in what’s coming next in chip technology.

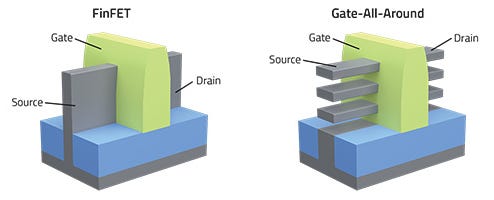

Advanced logic is always an area of interest. The finFET, which represents today’s high-performance transistor technology, is reaching its performance limits. Nanosheet-based transistors, which will follow the finFET, are key to continuing Moore’s Law scaling. Nanosheets are GAA-based transistor architectures, where stacks of silicon channels are surrounded by the gate. They offer better electrostatic control than FinFETs, relatively high drive currents, and variable widths.

FinFET vs. Gate-all-around transistors Source: Lam Research

At IEDM, TSMC will present details on its forthcoming 2nm process, which represents the company’s most advanced technology. TSMC’s new 2nm process, called N2, represents the company’s first technology based on GAA nanosheet transistors. (Click here for TSMC’s roadmap)

In the paper, TSMC will describe GAA transistors, middle-/back-end-of-line interconnects with the densest SRAM macro ever reported (~38Mb/mm2). The 2nm process offers a 15% speed gain (or 30% power reduction) at >1.15x chip density versus the company’s 3nm process, according to an abstract that describes the paper.

The high-density cells in TSMC’s 2nm (N2) process provide a 14%-15% speed gain over the company’s N3E technology across the Vdd range. TSMC’s N2 provides a 35% power savings at a higher voltage and a 24% power savings at a lower voltage.

TSMC’s N2 platform is currently in risk production and scheduled for mass production in the second half of 2025. TSMC’s N2P process, a 5% speed enhanced version of N2, is targeted for qualification in 2025 with mass production slated for 2026.

Meanwhile, at IEDM, Intel is expected to present a paper on a RibbonFET transistor technology with a 6nm gate length. RibbonFET is another name for GAA-based nanosheet transistors.

Intel will describe how it manufactured RibbonFET CMOS transistors with 6nm gate lengths at a 45nm contacted poly pitch with no degradation of electron mobility. “(Intel) will show that electron mobility doesn’t degrade until 3nm Tsi (silicon thickness), below which electron scattering due to surface roughness becomes an issue,” according to an abstract from Intel. “(Intel) will describe how they achieved good short channel control (≤100mV/V at <4nm Tsi), with extremely low threshold voltage at these gate lengths through workfunction engineering. The work shows that 3nm is a practical scaling limit for RibbonFETs.”

After the finFET runs out of steam at the 3nm node, nanosheet-based transistors are expected to be the next high-performance transistor for several years. What’s next?

The complementary FET (CFET) is one option. CFETs are integrated 3D designs, where n-FET and p-FET nanosheets are stacked on top of one other.

Last year at the IEDM, TSMC unveiled a monolithic CFET architecture for logic technology scaling. This year, TSMC will describe how it built the first fully functional advanced CFET inverter at a 48nm gate pitch.

There are other options for future chips. Carbon nanotube (CNT) FETs, 2D FETs and amorphous oxide semiconductors also offer the potential to continue to extend Moore’s Law.

At IEDM, a team led by Peking University will describe a CNT-based MOSFET. Researchers used high-density CNT arrays to build a 100nm gate-length MOSFET with saturated on-state current (Ion) of 2.45mA/μm and peak transconductance (gm) of 3.7mS/μm, resulting in a gm/Ion ratio>1.5.

At IEDM, Intel will present a paper on using 2D materials for future logic devices. The company will describe how they used 1) a gate-oxide atomic layer deposition (ALD) process; and 2) a low-temperature gate cleaning process.

With these processes, Intel build GAA devices that demonstrated breakthrough performance for MoS2- and WSe2-based GAA NMOS and PMOS transistors, respectively. This includes record sub-threshold slope (<75mv/dec) and drain current (Idmax>900 µA/µm at <50nm gate length) in sub-1nm-thick monolayer MoS2 GAA NMOS transistors.

Memory

Memory is also a hot topic at IEDM. There is still a lot of interest in next-generation ferroelectric memories.

At IEDM, SK Hynix will detail how they achieved analog computation in 3D vertical ferroelectric NAND (FeNAND) devices. The company used gate stack engineering techniques to improve the analog switching properties of 3D FeNAND cells, and achieved a ≥256-conductance-weight levels/cell. “The 3D FeNAND arrays improved analog CIM density by 4,000x versus 2D arrays, and demonstrated stable multiply-accumulate (MAC) operations with high accuracy (87.8%) and 1,000x higher computing efficiency (TOPS/mm2) versus 2D arrays,” according to SK Hynix in an abstract.

DRAM is the workhorse main memory technology in today’s systems. But it’s becoming more difficult to scale the DRAM.

At IEDM, a Kioxia-led team will describe a new type of 4F2 DRAM, The DRAM comprises of GAA IGZO (indium-gallium-zinc oxide) vertical channel transistors and a new integration scheme.

In addition, IGZO-based thin-film transistors (TFTs) have gained increasing interest for DRAM devices and for non-volatile DRAM replacements, due to their low leakage current. However, the electrical characteristics of IGZO TFTs, such as threshold voltage, can change over a device's lifetime, especially at elevated temperatures.

At IEDM, Imec will report on the results of studies it has made on the threshold voltage instabilities in IGZO TFTs. “These studies reveal that such instabilities are strongly dependent on factors like device architecture, channel deposition, IGZO stoichiometry and phase, and the waveform used during device operation,” according to Imec. “(Imec) identified two potential solutions to mitigate threshold voltage changes: using indium-poor films (In~5%) and restricting the duty cycle of the operating waveform to below 25%. These approaches are key enablers for development of future DRAM technology.”

New breakthroughs

Many of these and other devices will require new breakthroughs in terms of equipment and materials. In some cases, it will require high-NA EUV lithography. New metrology techniques and other fab processes are also needed. IC test is also key.

Not all devices require leading-edge processes. Chips manufactured in older 200mm fabs are still going strong. The same is true for mature package types.

In fact, IC-packaging is important. Many new chip architectures will require new and advanced packages. Chiplets are becoming a buzzword here.

In some cases, chipmakers will stack dies and bond them, resulting in 3D chips. New and different module technologies are also emerging.